-

Posts

753 -

Εγγραφή

-

Τελευταία Επίσκεψη

Content Type

Forums

Ειδήσεις

Reviews

Αγγελίες

Blogs

Gallery

Posts posted by astrovasilis

-

-

-

Βασικα πανο να σου εξηγησω.

Η L2 ειναι 2MB λογω των APUs που δεν εχουν L3 και λογω των servers.

H FPU στον PD δουλεύει περίπου όπως δουλεύουν τα IEU του του Hass με HT , σαν λογική εννοώ.Οχι το ΗΤ δουλευει στους κενους κυκλους του πυρηνα . Στον FX σε καθε κυκλο ο decoder στελνει και στα δυο νηματα. Μονο σε AVX εντολες εχουμε 256bit εντολες και το ενα ΙΕU να εχει ολη την FPU.

Ο FX εχει θεμα στο misprediction και μετα ( και ειναι ενας απο τους λογους του σημερινου single thread ) . Ο branch predictor ειναι σαν του sandy περιπου. Με τον SR θα φανει η δυναμη του πυρηνα

Τα θεματα του BD τα ξερανε απο το 2011 αλλα εδω μιλαμε για μεγαλες αλλαγες που θελουν αρκετο χρονο και μιλαμε για την AMD . Γι αυτο ηθελαν 2 χρονια με το APU kaveri.

-

Οταν χρειάζονται 128bit έχεις 8 FPU στους PD, την στιγμή που ο Hass μένει με 4 FPU των 128bit και το υπόλοιπο να κάθεται και να περιμένει = καταναλώνει ενέργεια ... Εδώ το CMT είναι ανώτερο από το HT στο κομμάτι performance /watt θεωρητικά τουλάχιστον και δεν δεσμεύει χώρο πολύ ενώ είναι πλήρως χρηστικό σε κάθε κατάσταση. Εδώ η AMD θα αλλάξει αρκετά πράγματα στους SR για καλύτερη απόδοση. Τουλάχιστον αυτά έχουν πει.

Σε οκτω νηματα εχει ο FX 2 Χ4 128bit FMAC ναι. Φαντασου ομως οτι η ιντελ ειναι στα 22nm και η AMD στα 32 28nm. Η AMD το εκανε λογω χωρου και λογω HSA.

Το σχετικο μεγεθος της FPU στον SB ειναι αλλο απο του module του FX.

http://www.guru3d.com/articles_pages/amd_fx_8350_8320_6300_processor_4300_performance_review,3.html

Επισης οταν εχεις 2MB L2 το perf/w ειναι αστο. Φαντασου σε δυο νηματα θες 4MB L2 ενω στους PH II 1MB και στους SB 512KB.

This seems quite legit and it's a big module indeed.... It seems many resources are doubled:

This seems quite legit and it's a big module indeed.... It seems many resources are doubled:Floating point:dual 256 bit FMA instead of dual 128 bit FMA.

Integer:8 ALU's and 8 AGU's instead of 4 both. Dual 32kB data caches instead of dual 16 kB.

Many other resources are also doubled like rename hardware and so on.

οχι οχι δεν γινονται αυτα απο την AMD. Η ιδια ειπε για πειραγμα τους front end.

http://www.anandtech.com/show/6201/amd-details-its-3rd-gen-steamroller-architecture

Με βάση τα δομικά στοιχεία του module και όχι τις ασθένειες του είναι ισχυρότερο. 4ALUS +4AGUS ενώ ο SB έχει 3+3 ! Απλά ο SB παίζει με 3 και σε single ενώ ο PD παίζει με 2 μέχρι 4 νήματα ...μετά μπαίνουν τα άλλα 2 όσο γεμίζουν οι 2οι πυρήνες του module.Και ο PH II 3 ALUs ειχε.

Πραγματικα με τον SR θα ηθελα να παρατηρησω τη πραγματικη δυναμη του ( νεου ) module. Στανταρ μιλαμε για 10% καλυτερο πυρηνα

Although AMD doesn’t like to call it a cache, Steamroller now features a decoded micro-op queue. As x86 instructions are decoded into micro-ops, the address and decoded op are both stored in this queue. Should a fetch come in for an address that appears in the queue, Steamroller’s front end will power down the decode hardware and simply service the fetch request out of the micro-op queue. This is similar in nature to Sandy Bridge’s decoded uop cache, however it is likely smaller. AMD wasn’t willing to disclose how many micro-ops could fit in the queue, other than to say that it’s big enough to get a decent hit rate. -

Το κάθε module βεβαίως είναι ισχυρότερο από του hass

οχι το module ειναι επιπεδου SB συν πλην.

Το θεμα ειναι οτι η υπαρξη διπλου decoder θα παει τα πραγματα σε Χ8 καταστασεις και οχι επι 6.5 αρα θα μιλαμε για οκταπυρηνο επεξεργαστη ( συν 20% ). Το θεμα ειναι τι ειδους FPU θα εχει ο SR ( ειπαν θα ειναι προσαρμοσμενη στις συγχρονες εφαρμογες ) και ποσο καλυτερος θα ειναι ο πυρηνας.

-

-

Σε multi καπου 25%. Σε single δε ξερουμε καπου 10% λεω.

-

-

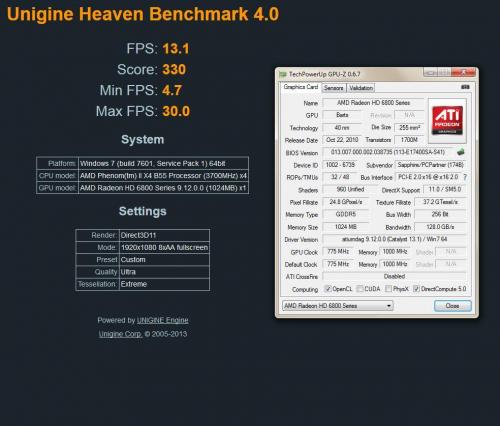

[MENTION=17377]sol1d[/MENTION] Στο heaven 4.0 ποσα καρε ειναι η 460;

-

-

[MENTION=1621]Ν.Ι.Κ.Κ.[/MENTION] , [MENTION=1199]Volrath[/MENTION] 6850 στα 900ΜΗΖ.

-

-

[MENTION=9179]atiman[/MENTION]

Θα πρεπει ομως να καταννοηθει οτι οι λογοι που οδηγησαν το team να αυξησει την αποδοση των καρτων με τους 12.11 μπορει και να μην ηταν τα fps με το πραγματικο αριθμητικο τους μεγεθος.Μας λες οτι κατι κανατε στις 12.11 και μεταξυ των αλλων ηταν και το συν 5 -10% των fps;

Η να περιμενουμε και ακομα κατι αλλο σε αυξηση επιδοσεων αυριο;

-

Σε single thread θελει συν 700ΜΗΖ ο BD απο τον PH II.

-

-

[MENTION=28502]darkiller[/MENTION] Δεν ειναι σταθερος.

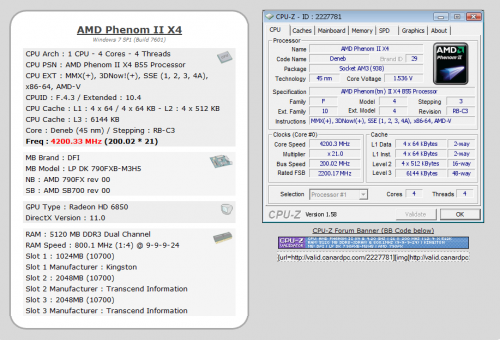

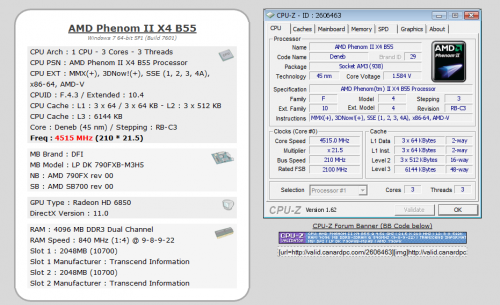

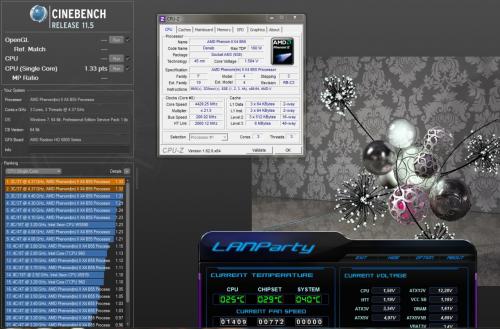

Σταθερος με τεσσερεις πυρηνες ειναι στα 4200ΜΗΖ με 1.58V ( ποσο σταθερος δε ξερω ) αλλα θελει συν 200W χωρις την αποδοση του τροφοδοτικου.

Με τρεις πυρηνες ειναι στα 4380ΜΗΖ( ποσο σταθερος δεν ξερω ) με 1.58V.

-

AMD PH II 555 σε 955 ( Β55 )

-

-

Με αλλα λογια ειναι χειροτερα τα 250GB του 840 απο του 830;

Το καθε cell MLC θελει 2bit και σε TLC 3 bit; Και σε SLC ενα bit;

-

Για να καταλαβω το BW του 840 ειναι της ταξης του DDR2 και το BW toy 830 του DDR1 ή χρησιμοποιουν τη τεχνολογια αυτη;

-

Target-Independent Rasterization (TIR): TIR is a new rendering path that enables superior anti-aliasing in Direct3D driver applications

Optimized GPU power consumption

Καλυτερο AA se WIn 8 και διαχειριση ενεργειας;

-

^

This release of AMD Catalyst™ 12.7 Beta includes a number of performance optimizations for the AMD Radeon ™ HD 7900, AMD Radeon HD 7800, and AMD Radeon HD 7700 Series. -

[MENTION=9179]atiman[/MENTION] κατι αντιστοιχο με το adaptive Vsync θα φτιαξει η ΑΤΙ;

-

[MENTION=21908]dimi123[/MENTION]

Ωραιο

Εκει που λεει εγραφα εφαρμογες κτλ πως το κανες;

Επισης εκει πανω που λεει youtube κτλ πως τοκανες;

Επισης αυτο με το καιρο ποιο ειναι;

-

Απο 6950 και πανω...

AMD STEAMROLLER ! Νεότερα ,φήμες, αρχιτεκτονική, επιδόσεις.

In AMD Platform