Samsung και Kingston ανεβάζουν τις τιμές SSD πάνω από 10% — και άλλοι κατασκευαστές θα ακολουθήσουν

Ταυτόχρονη κίνηση από δύο κολοσσούς

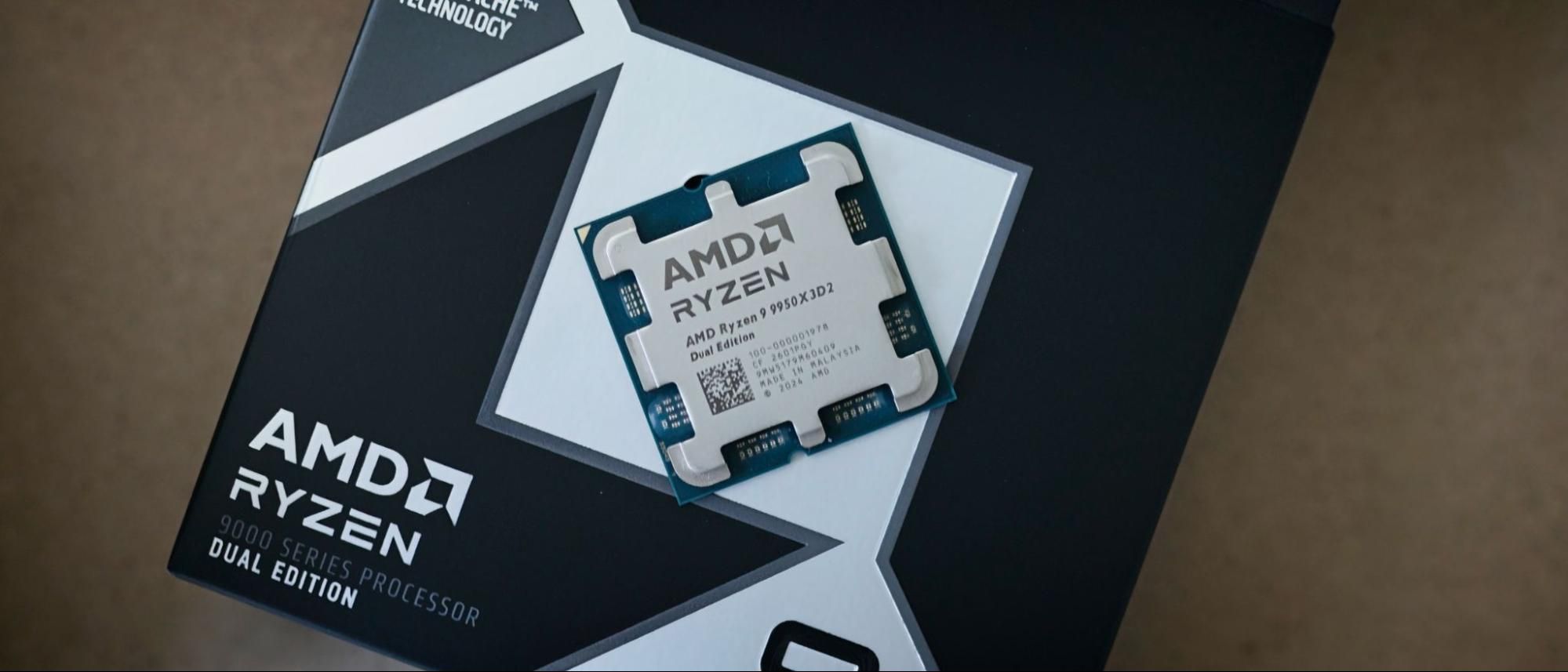

Σύμφωνα με τα πιο πρόσφατα δεδομένα, η Samsung έχει ήδη εφαρμόσει τις νέες υψηλότερες τιμές, ενώ η Kingston εφαρμόζει παρόμοια αύξηση σε ολόκληρο το χαρτοφυλάκιο SSD της στο ίδιο χρονικό πλαίσιο. Η Samsung, ως ο μεγαλύτερος παγκόσμιος κατασκευαστής NAND flash, διαδραματίζει κεντρικό ρόλο στον καθορισμό των τάσεων τιμολόγησης σε ολόκληρο τον κλάδο, ενώ η Kingston διατηρεί δεσπόζουσα θέση στην αγορά consumer SSD και μνήμης.

Όταν κατασκευαστές αυτής της κλίμακας προσαρμόζουν τις τιμές ταυτόχρονα, οι επιπτώσεις σπάνια περιορίζονται σε ένα μόνο επίπεδο. Αντίθετα, σηματοδοτούν συνήθως μια ευρύτερη μεταβολή στις συνθήκες της αγοράς, που επεκτείνεται μέσα από τα κανάλια διανομής ως και στη λιανική τιμολόγηση.

Το NAND σε ελεύθερη πτώση προς τα... πάνω

Τα νούμερα είναι εντυπωσιακά: η Kingston έχει αναφέρει αύξηση 246% στις τιμές NAND wafer σε σχέση με το Q1 του 2025, με το 70% αυτής της αύξησης να έχει συγκεντρωθεί μέσα στις τελευταίες 60 μόλις μέρες. Δεδομένου ότι τα chips NAND flash αποτελούν περίπου το 90% του κόστους κατασκευής ενός SSD, η κατάσταση είναι ιδιαίτερα ανησυχητική τόσο για τις επιχειρήσεις όσο και για τους καταναλωτές.

Σε αριθμούς αγοράς, τα NVMe SSDs έχουν δει αυξήσεις κοντά στο 115% και τα SATA SSDs άνω του 75% από τα χαμηλά τους. Ενδεικτικά, το Kingston NV3 2TB εκτινάχθηκε από τα $150 στα $380 (αύξηση 153%), ενώ το Samsung 990 Pro 2TB από τα $190 στα $400, ξεπερνώντας το 111%.

Γιατί συμβαίνει αυτό;

Οι συνθήκες αγοράς υποδηλώνουν ότι οι προσαρμογές τιμών αποτελούν μέρος μιας μεγαλύτερης τάσης που επηρεάζει τη δυναμική προσφοράς και ζήτησης NAND flash. Είτε οφείλεται σε αυξημένο κόστος παραγωγής, είτε σε περιορισμούς προσφοράς ή στρατηγική ανάκτηση περιθωρίων κέρδους, το αποτέλεσμα είναι μια συνεχής σύσφιξη τιμολόγησης στο τμήμα αποθήκευσης.

Βασικός παράγοντας είναι η τεράστια ζήτηση από το AI και τα data centers: η Samsung και η SK Hynix μείωσαν την παραγωγή NAND wafers για το 2026 σε σχέση με το 2025, ενώ παράλληλα αναδιατάσσουν παραγωγή προς enterprise και server SSDs σε βάρος των consumer προϊόντων. Η Kioxia έχει ήδη αναφέρει ότι ολόκληρος ο όγκος παραγωγής NAND flash για το 2026 έχει ήδη προπωληθεί.

Και άλλοι θα ακολουθήσουν

Υπάρχει ισχυρή πιθανότητα να ακολουθήσουν και άλλοι κατασκευαστές SSD με παρόμοιες αυξήσεις. Σε ανταγωνιστική αγορά, η διατήρηση τιμών σημαντικά χαμηλότερων από τους μεγάλους προμηθευτές δημιουργεί πίεση στα περιθώρια, καθιστώντας δύσκολη τη μακροπρόθεσμη βιωσιμότητα. Ως εκ τούτου, πρόσθετοι κατασκευαστές ενδέχεται να ευθυγραμμίσουν τις στρατηγικές τιμολόγησής τους βραχυπρόθεσμα.

Για τους καταναλωτές και τους system builders, αυτές οι αυξήσεις μπορεί να επηρεάσουν το συνολικό κόστος νέων PC builds και αναβαθμίσεων, ιδιαίτερα σε διαμορφώσεις που απαιτούν αποθήκευση υψηλής χωρητικότητας ή υψηλής απόδοσης. Αν οι τρέχουσες τάσεις συνεχιστούν, η αγορά SSD ενδέχεται να παραμείνει σε υψηλότερο επίπεδο τιμολόγησης για το ορατό μέλλον, με αναλυτές να μιλούν για πιθανή ανακούφιση μόλις το 2027-2028.

Τι πρέπει να κάνεις τώρα;

Η σύσταση από στελέχη του κλάδου είναι σαφής: αν σκέφτεσαι αναβάθμιση αποθήκευσης, η καλύτερη στιγμή είναι τώρα. Οι τιμές αναμένεται να συνεχίσουν να ανεβαίνουν, και η αναμονή πιθανότατα δεν θα επιφέρει οικονομία. Αξίζει να αναζητήσεις τιμές από πολλαπλούς retailers και να εκμεταλλευτείς τυχόν διαθέσιμο stock σε τρέχουσες τιμές.

Πηγές

Guru3D – Samsung and Kingston Trigger New SSD Price Hike Above Ten Percent PC Gamer – Kingston sounds the SSD pricing alarm GamersNexus – SSDs: WTF? TweakTown – Samsung halting SATA SSD production

483