Η Intel «εκβιάζει» τους κατασκευαστές PC: Πάρτε τα 18A chips ή μείνετε χωρίς επεξεργαστές

Παραγγελία 100 chips, παράδοση 30 — και 10 από αυτά ανεπιθύμητα 18A

Η πρακτική αυτή αποτυπώνεται με ανησυχητική σαφήνεια στην κατάθεση στελέχους κατασκευαστή PC που παρέθεσε το Nikkei. Το στέλεχος ανέφερε ότι η εταιρεία του παρήγγειλε 100 επεξεργαστές βασισμένους στον κόμβο Intel 7, αλλά παρέλαβε μόλις 30 — εκ των οποίων οι 10 ήταν 18A. Η Intel, σύμφωνα με την ίδια αναφορά, ξεκαθάρισε ότι αν οι εταίροι δεν αποδεχθούν τα chips 18A, αυτά θα διατεθούν σε άλλον πελάτη, χωρίς αντικατάστασή τους από τους αρχικά παραγγελθέντες επεξεργαστές Intel 7.

Το σενάριο αυτό δεν είναι τυχαίο. Η Intel έχει στηρίξει την ανάκαμψή της για το 2026 στους κόμβους 18A και 14A, με τα Panther Lake, Nova Lake και Diamond Rapids να αντιμετωπίζουν στενά χρονοδιαγράμματα εκτέλεσης. Ταυτόχρονα, υπάρχει μια ασυμμετρία: η Intel χρησιμοποιεί τον 18A για τα laptop Panther Lake χαμηλότερου όγκου, ενώ τα desktop chips Nova Lake υψηλότερου όγκου τα αναθέτει στη TSMC.

Επανασχεδίαση προϊόντων και καθυστερήσεις κυκλοφορίας

Η μετάβαση στα chips 18A δεν είναι ουδέτερη για τους κατασκευαστές. Η χρήση των νέων επεξεργαστών επιβάλλει ολική επανασχεδίαση των προϊόντων, ώστε να δικαιολογηθούν οι υψηλότερες τιμές στους καταναλωτές. Αυτή περιλαμβάνει χρήση οθονών υψηλότερης ποιότητας και άλλων εξαρτημάτων, σε μια διαδικασία που καθυστερεί επίσης τα χρονοδιαγράμματα κυκλοφορίας των προϊόντων, σύμφωνα με τους συμμετέχοντες στη βιομηχανία.

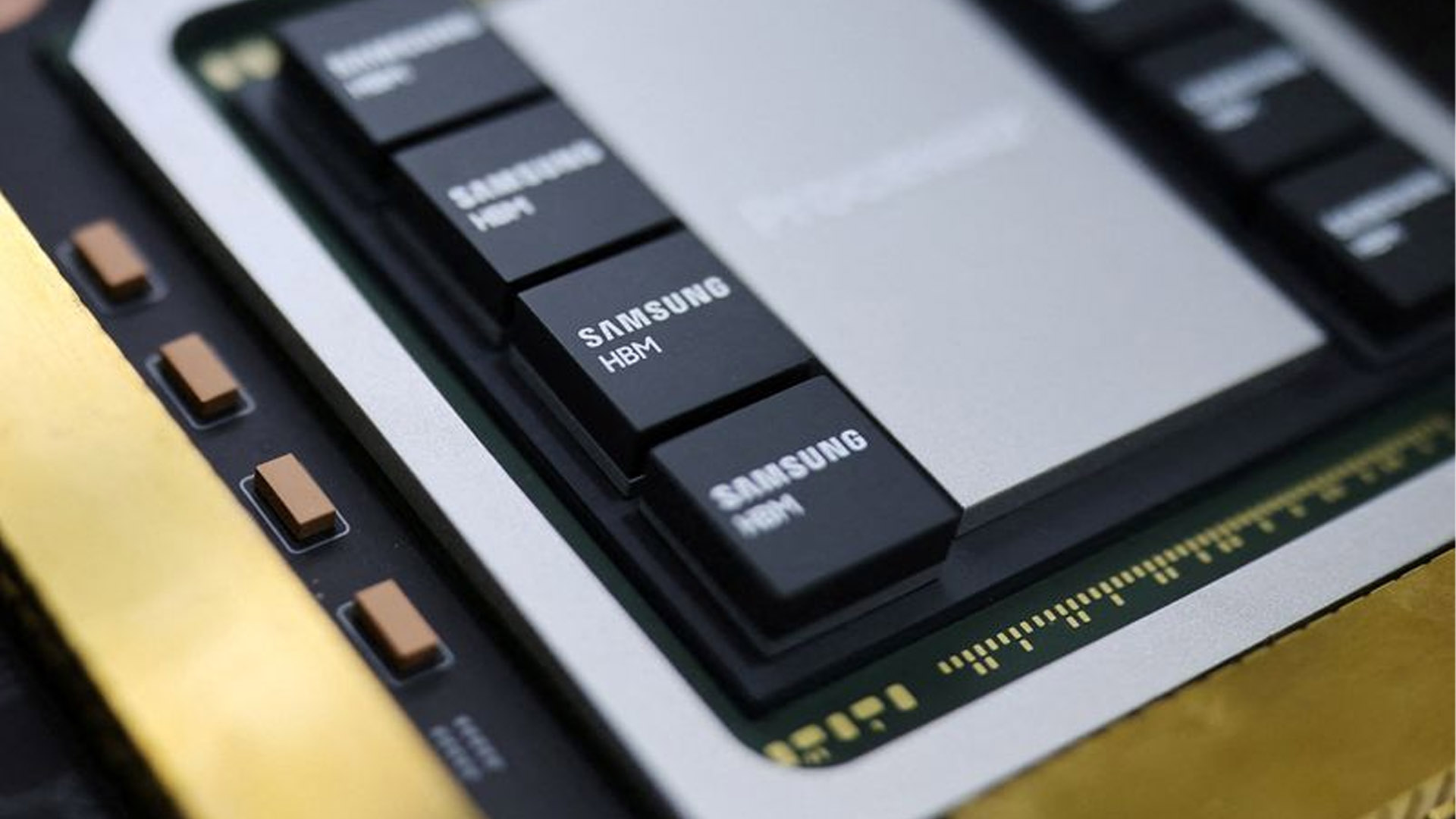

Σύμφωνα με ανάλυση της TechInsights, το σύστημα τροφοδοσίας από την πίσω πλευρά (BSPDN — Backside Power Delivery Network) που χαρακτηρίζει τον 18A αποτελεί πλήρη επανασχεδίαση της φυσικής διάταξης του chip, αναγκάζοντας τους πελάτες να ξαναδουλέψουν από την αρχή τις καθιερωμένες μεθοδολογίες σχεδιασμού. Ωστόσο, ακόμα και στις αρχές του 2026, οι βιομηχανικοί εταίροι παραμένουν αργοί στη δέσμευση, αντικατοπτρίζοντας πόσο διαταρακτική είναι η νέα αρχιτεκτονική της Intel.

Το 18A ως εργαλείο αναζωπύρωσης του foundry business

Η προώθηση των πιο σύγχρονων chips γίνεται καθώς η Intel στοχεύει να χρησιμοποιήσει την «κούρσα» της τεχνητής νοημοσύνης για να ανακτήσει την πρωτοπορία της στην παραγωγή προηγμένων chips, έχοντας υστερήσει σημαντικά έναντι της TSMC στην εκμετάλλευση της έκρηξης ζήτησης για AI.

Η εικόνα βελτιώνεται, έστω σταδιακά. Στο τηλεφώνημα αποτελεσμάτων Q1 2026, ο CFO David Zinsner επιβεβαίωσε ότι οι αποδόσεις παραγωγής (yields) του κόμβου 18A παρακολουθούν πορεία που θα φτάσουν τους στόχους τέλους έτους ήδη από τα μέσα του 2026 — περίπου δύο τρίμηνα νωρίτερα από το προηγούμενο πρόγραμμα. Παράλληλα, οι αποδόσεις του Intel 18A συνεχίζουν να βελτιώνονται καθώς αυξάνεται η προσφορά για να καλυφθεί η ισχυρή ζήτηση πελατών, ενώ η ανάπτυξη του 14A παραμένει σε τροχιά.

Στο μέτωπο των εξωτερικών πελατών, η στρατηγική μοιάζει να αποδίδει. Ο CFO Zinsner δήλωσε στο Morgan Stanley Technology, Media & Telecom Conference 2026 ότι ο CEO Lip-Bu Tan, αν και αρχικά σκεφτόταν να κρατήσει τον 18A ως αποκλειστικά εσωτερικό κόμβο, πλέον αρχίζει να αναγνωρίζει ότι αποτελεί καλό κόμβο για προσφορά σε εξωτερικούς πελάτες. Η εταιρεία δέχεται εισερχόμενο ενδιαφέρον για τον 18A-P ως κόμβο foundry — κάτι που ο CFO χαρακτήρισε «αρκετά θετικό».

Η Intel παρουσίασε την οικογένεια επεξεργαστών Core Ultra Series 3, την πρώτη πλατφόρμα AI PC που βασίζεται στον κόμβο 18A, η οποία αναμένεται να τροφοδοτήσει πάνω από 200 σχεδιασμούς από κορυφαίους κατασκευαστές παγκοσμίως, καλύπτοντας από premium έως mainstream laptops, gaming handhelds, ρομποτική και βιομηχανικές συσκευές.

Το μεγάλο ερώτημα παραμένει αν οι εταίροι κατασκευής PC θα αντέξουν το οικονομικό βάρος της επανασχεδίασης — και αν ο τελικός καταναλωτής θα είναι διατεθειμένος να πληρώσει το αντίτιμο αυτής της στρατηγικής επιλογής της Intel.

Πηγές

WCCFTech — Intel Strong-Arms PC Partners Into Buying 18A Chips (19/5/2026) Investing.com / Nikkei Asia — Intel pushes PC makers to adopt latest CPUs (19/5/2026) Tom's Hardware — Intel CEO embraces 18A node for external customers (5/3/2026) TechSpot — Intel's 18A process works, now it has to convince the industry (10/2/2026) TechTimes — CPU supply crunch: Intel, AMD, Arm racing to fill the gap (15/5/2026)

548